57684 - Vivado Simulation - How do I back-annotate an IP with a functional simulation model in a behavioral simulation?

66533 - Simulation - What files are needed to simulate Vivado IP in standalone Third party simulator?

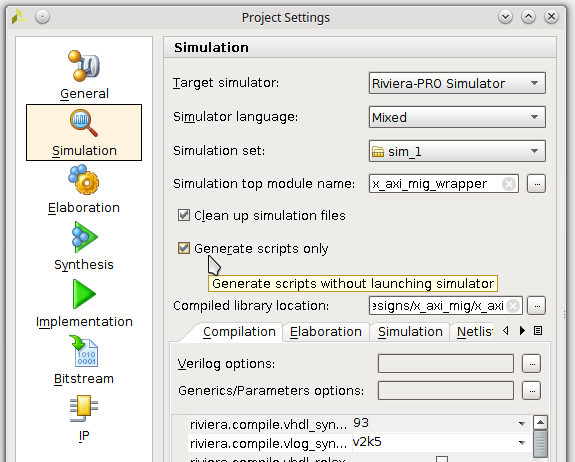

Accelerating Simulation of Vivado Designs with HES - Application Notes - Documentation - Resources - Support - Aldec